前面的文章对SRAM的Cache做了详细分析,而这部分将对另一种随机存取器动态随机存储器DRAM做进一步说明。本文大部分是基于BranchEducation的视频内容和其它文章进行行文的,文章截图全部来自视频,部分是自己所画,视频连接放在最后的参考资料部分。

DRAM

DRAM:Dynamic Random Access Memory,动态随机存储器。

在DRAM的分类中,SDRAM(Synchronous DRAM)同步动态随机存储器在各个行业则占较大的比例。而我们经常听到的DDR(Double Data Rate SDRAM)即双倍速率SDRAM则又是SDRAM中的主要代表,本篇将着重对DDR原理进行分析

DRAM是程序运行的和临时数据存储的媒介,无论是计算机还是手机的参数主存大小即指的是DRAM的大小。在工作中我们其实很少区分DDR和DRAM,严格来说DDR只能是DRAM中的一种,whatever,工作中不影响正常理解和使用就好。

DDR SDRAM

简介

DDR SDRAM:Double Data Rate Synchronous Dynamic Random Access Memory,双倍数据率同步动态随机存取存储器。之所以“同步”是指内存的工作需要同步时钟,命令的发送和数据的传输都要以此为基准;“动态”则是因为我们需要为其提供电压定时刷新来保证数据的完整性,掉电则数据丢失;“双倍”则是由于其在时钟的上升沿和下降沿都可以进行数据的传输

LPDDR SDRAM:Low-Power Double Data Rate SDRAM,是一种功耗较低的同步动态随机存取存储器,主要用于移动计算机和手机等设备。较旧的变体也称为移动 DDR,缩写为 mDDR。现代 LPDDR SDRAM 与DDR SDRAM截然不同,具有多种差异,甚至LPDDR 技术标准是独立于 DDR 标准开发的。(本篇不对此做详细说明)

各版本参数对比

| DDR SDRAM Standard | Bus clock (MHz) | Internal rate (MHz) | Prefetch (min burst) | Transfer Rate (MT/s) | Voltage | DIMM pins | SO-DIMM pins | MicroDIMM pins |

|---|---|---|---|---|---|---|---|---|

| DDR | 100–200 | 100–200 | 2n | 200–400 | 2.5/2.6 | 184 | 200 | 172 |

| DDR2 | 200–533 | 100–266 | 4n | 400–1066 | 1.8 | 240 | 200 | 214 |

| DDR3 | 400–1066 | 100–266 | 8n | 800–2400 | 1.5 | 240 | 204 | 214 |

| DDR4 | 800–1200 | 200–300 | 16n | 1600–5067 | 1.2 | 288 | 260 | 214 |

概念

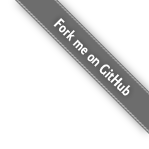

channel:通道,属于控制器端的概念。可以简单理解为一个通道对应一个DDR控制器,每个通道拥有一组地址线、控制线和数据线

SIMM:Single In-line Memory Module,单列内存模组。内存模组电路板与主板插槽的接口只有一列引脚

DIMM:Double In-line Memory Module,双列内存模组,主板上的一个内存插槽,内存模组电路板与主板插槽的接口有两列引脚。一个Channel可以包括多个DIMM。

Rank:CPU在一个时钟周期取数据的大小取决于数据总线的位宽(这个位宽被称为物理 Bank(Physical Bank),通常内存颗粒都没有P-Bank大小的位宽,这时就需要多个内存颗粒组合起来满足CPU的一次访存。假设P-Bank=64bit即64位数据总线,而内存颗粒Chip的位宽是8bit,则8个chip组成了一个Rank。

Chip:1个chip大多是4bit/8bit/16bit等,多个chip组成一个rank,配合完成一次访问的位宽要求。这就是颗粒。内存颗粒共享地址和命令总线,各自有自己的数据总线

Bank:也称Logic Bank逻辑Bank,与物理bank的概念相对应。由于成本、技术以及SDRAM工作原理的限制,做一个全容量的Bank不太现实(寻址冲突),所以在寻址时需要先选中Bank,在根据行列选中数据。DDR2、DDR3已经有8个Bank

row/column:行列,存储的最小单元,每一个行列交叉点存储了1bit的数据。

笼统上讲从大到小为:channel > DIMM > rank > chip > bank > row/column,如下图:

内存大小

SDRAM总存储容量 = 行数 x 列数 x L-Bank数量 = 存储单元个数 x 存储单元容量(4bit/8bit/16bit)

基本结构

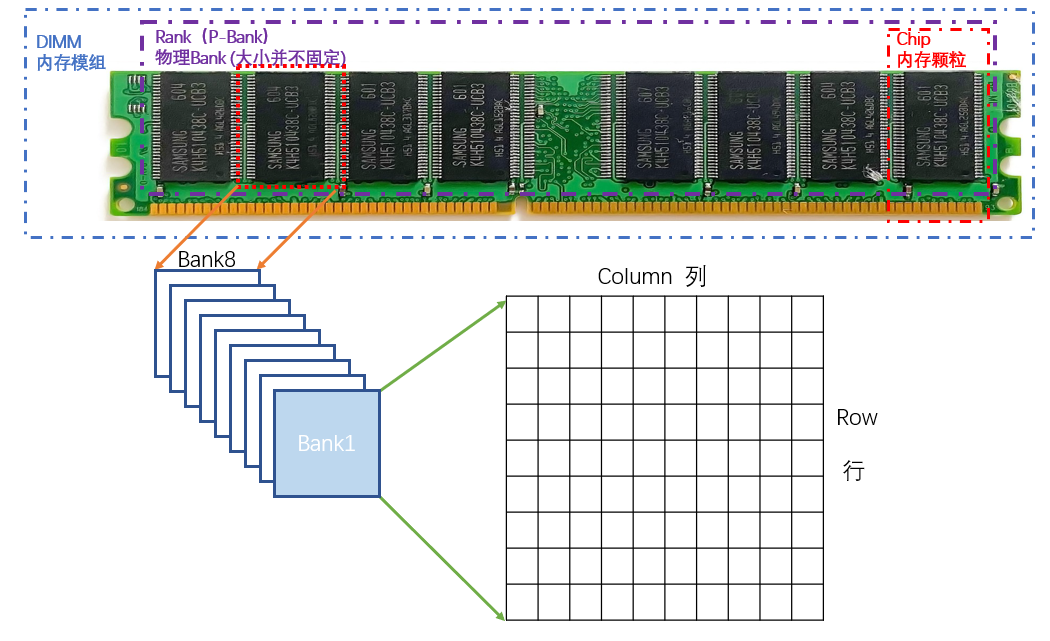

Tips:判断MOS管是N沟道还是P沟道,里N外P,即箭头指向G是NMOS,反之是PMOS

利用了电容能够保持电荷及其充放电的特性。目前市场最常用的存储1bit数据的SDRAM的结构是由一个MOS管、一个电容和两根导线组成的。电容一段连接晶体管一端另一端接地、字线连接MOS管的栅极,位线连接到晶体管通道的另一端,如下图所示:

写

当字线(WL)电压为逻辑1时开关打开,存储单元选通,如果此时位线(BL)为高电压,则向电容中充电,则就是向存储单元中写1;相反如果WL=1,BL=0电容放电,这就是向存储单元中写0

读

当字线(WL)电压为逻辑1时开关打开,此时在位线上连接电量计就可以测量电容中存储的的值。如果电容放电,那么就表示这个单元里原来存的值是 1,如果电容不放电,则表示原来的值是 0。可见当DRAM进行数据读取的时候会使存储单元中的1变成0,是有破坏性的,而实际中我们需要读出继续保持数据或电荷,后面有对此的解决办法(感应放大器)

当字线关闭的时候就不进行任何读写操作了,晶体管也紧跟着被关闭,电容器与位线隔离从而保存了之前写入的数据或电荷。但是由于晶体管十分小,存储在电容器中的电荷会在通道上慢慢泄露,因此又需要另外的技术来对此进行修复(Recharge)

工作原理

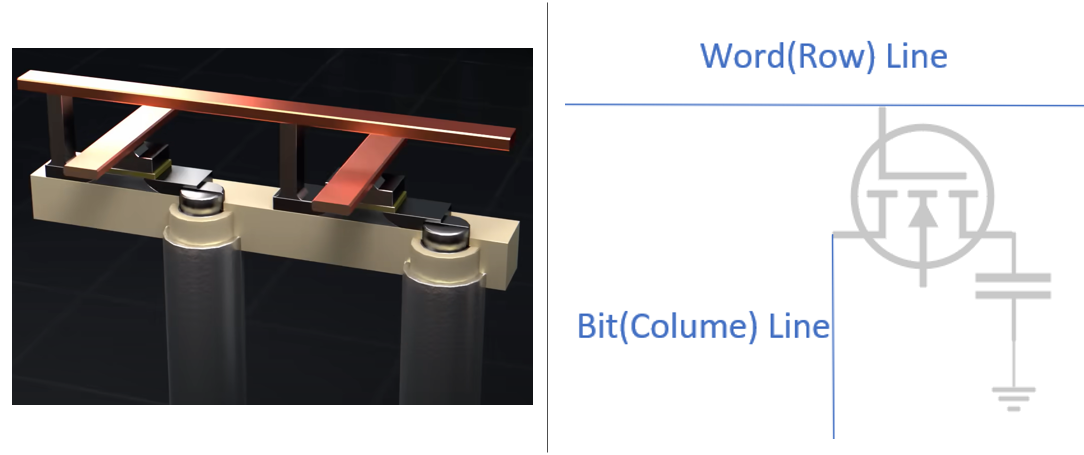

下图是对一个bank的一部分作图进行说明。行译码器、列选择复用器之所以这样设计是因为:当数据进行读写的时候,只需要打开某一个固定行(其它行关闭)即可,这样子该行所在的电容将连接到位线上,而在进行列选择的时候,由于是进行多比特的选择(4bit/8bit)所以要这里的列多路复用器相当于列中的第几组(组数*位宽)

读/写

通用流程

预充电电压根据DDR每一代是有所不同的,但一定是充电电压的一半

- 选择bank;

- 关闭所有行;关闭所有字线,隔离所有电容

- 预充电;将所有位线的电压升值供电电压一半(DDR5:0.55V;DDR4:0.6V;DDR3:0.75V)

- 行选择;字线上电打开MOS管形成的开关,电容连接到对应的位线

- 列选择;位线通过多路复用选择器连接到数据线上

说明

读(保证数据不丢失)

行选择时,当字线选中后,该行所在的电容被连接到对应的位线。如果电容存储的数据是1(电容压差是供电电压1.1 / 1.2 / 1.4),由于位线预充电后电压至供电电压的一半,所以电荷将从电容流向位线,进而位线电压增加,这时位线下面所连接的感应放大器能感受到这种轻微的变化或扰动,并放大这一变化,将位线电压再增加到供电电压(1.1 / 1.2 / 1.4);相反,如果存储的是0,电荷将从位线流向电容,位线电压降低,感应放大器放大这一变化,将位线电压降低至0V。这样就保证了既能够通过位线读取数据又保证电容数据不丢失

写

写流程与读类似,但当要写入的数据–>数据总线–>写驱动器器–>多路选择复用器–>感应放大器—>位线 这样流程下来的时候,由于写驱动器的存在,它比感应放大器强大的多,这将会导致写驱动器出来的数据直接覆盖掉位线上原有的数据

实例

假设32位地址总线,32个bank,65536(2^16^)行,8192(2^13^)列,8bitddr颗粒

- 0-4,5位地址将选择某个bank

- 行关闭 + 预充电

- 5-21,16位选择某个行

- 22-31,10bit选择某个组(每一组8列,这个由L-bank位宽决定)

刷新Refresh

refresh每一行的刷新时间是50ns。而整个bank刷新的时间间隔是64ms/次(小于电荷泄露1->0的最短时间)

目的

由于SDRAM最小存储单元电路形式是电容,电容是有自放电的特性。长时间存储电容电荷会漏电,故需要刷新和预充电进行补充。

分类

- 自动刷新(Auto Refresh,简称AR/REF,需要CK,CKE高)

- 自刷新(Self Refresh,简称SR/SRE-SRF,SDRAM内部产生,不依赖CK,CKE低,用于休眠模式或低功耗)

步骤

- 关闭所有行

- 预充电

- 打开行,感应放大并填充电荷

- 从第一行到最后一行重复第3步骤

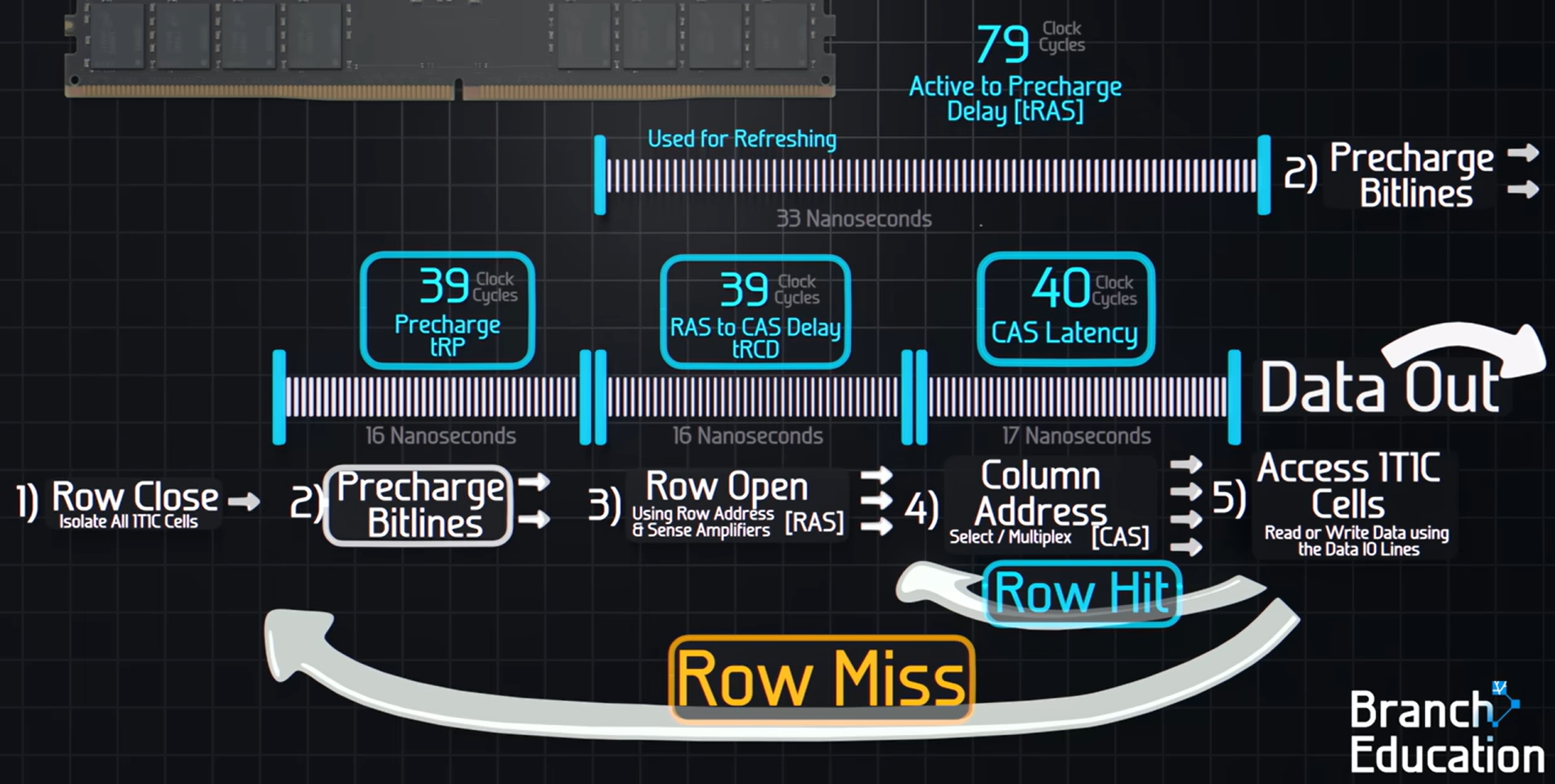

参数

- CAS:Column Address Select,列地址选择

- RAS:Row Address Select,行地址选择

- CAS Latency:(CL)CAS延迟。指的是从行打开到到接收到存储在列中的数据的时间

- tRCD:RAS to CAS Delay RAS-CAS延迟,激活时间。指的是在字线全部关闭,位线被预充电的情况下,打开一行所需要的时间

- tRP:RAS Precharge Time ,行预充电时间。指的是再打开一行之前对位线进行预充电的时间

- tRAS:激活一行和接下来预充电之间的时间

优化/访存加速

行命中

在DRAM的读写过程中,其中比较耗时的步骤应该就是行打开。

可以考虑这样一个场景:CPU第一次访存是在249行,第二次所需要的数据大概率也可能在249行,因此在第一次和第二次访存中间我们就可以不关闭行了,而是等到新的行访存再进行整个读写步骤。进而将一个bank内的情况推广到整个内存颗粒,每一个bank上都存在一行未关闭(即上次访存数据所在的行),而当下次访存所在的行如果打开则成为Row Hit行命中,如果没有称为Row Miss(参考【5参数】章节的图片)

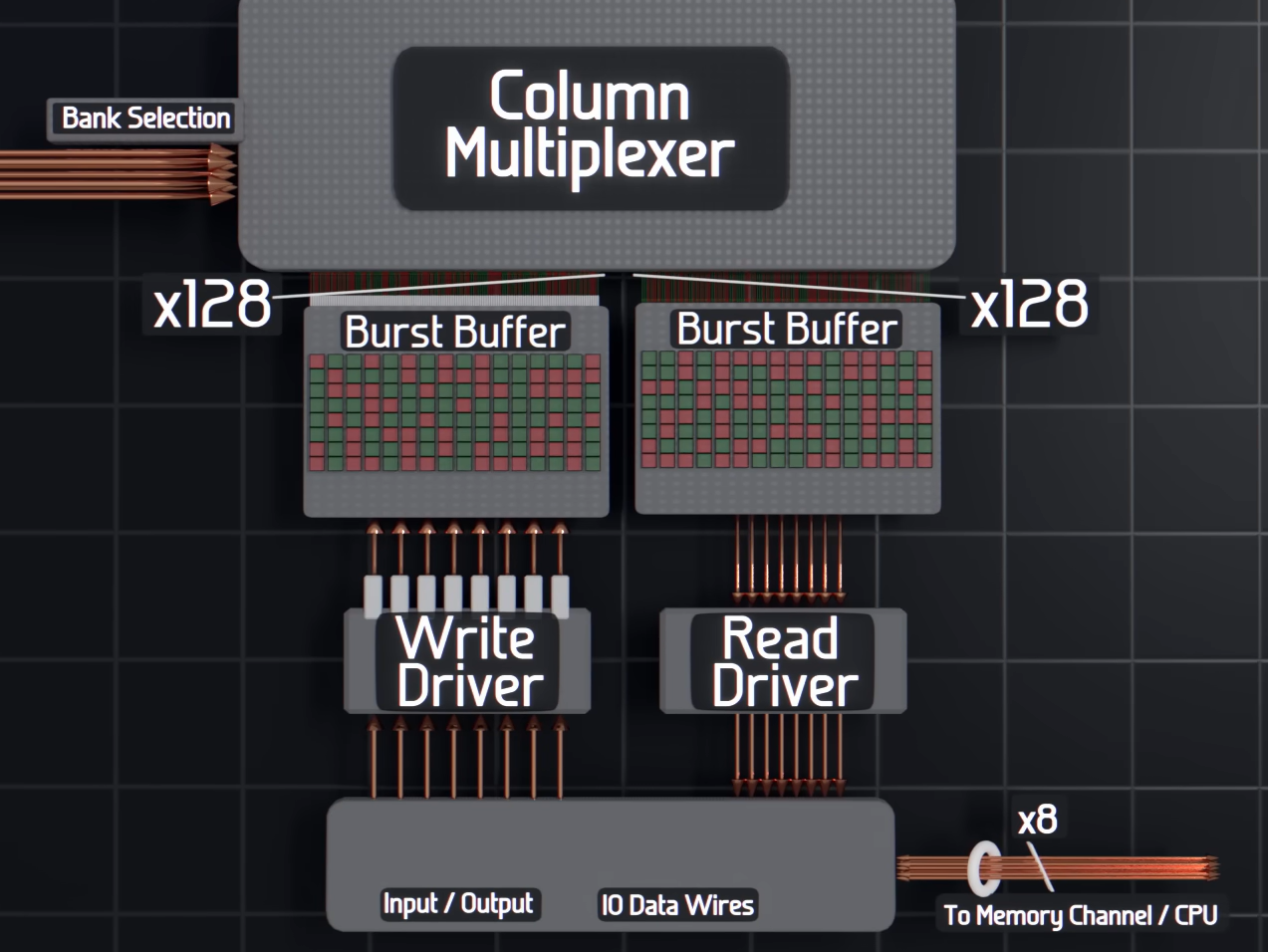

Burst Buffer

Burst:突发,是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(Burst Lengths,简称 BL)。

如果所示就是两个128bit的burst buffer,上端连接列选择即数据段,下面连接读写驱动器。人们只要指定起始列地址与突发长度,内存就会依次地自动对后面 相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。这样,除了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是 tRCD+CL)外,其后每个数据只需一个周期的即可获得。

至于 BL 的数值,也是不能随便设或在数据进行传输前临时决定。一定要参考相应的数据手册进行设置,比较常见的设定是 4 和 8。

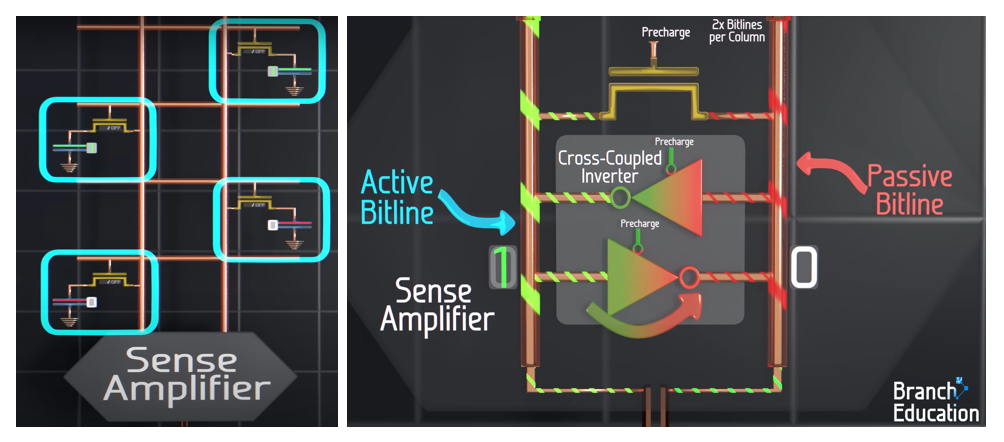

感应放大器

优化方式

让每一个感应放大器上由两个位线连接到其上,让交替排列的存储单元分别连接在左侧和右侧的位线。交叉耦合反相器的存在使得一半的位线处于1,另一半处于0,这被称为差分对

好处:

- 预充电时,由于差分对两侧一边是0,一边是1,所以断开两个反相器然后通过三极管将两个位线连接,电压将降低到中值

- 抗噪音

- 减少位线寄生电容

参考链接

1、2链接为同一视频,区别在于1是Youtube英文版,2是B站中文译版