基础

SPI:Serial Peripheral Interface 串行外设接口,用于在微控制器和外部设备之间进行数据传输。SPI 接口广泛应用于嵌入式系统中,特别是与外围设备进行通信,如传感器、存储器、显示屏和通信模块等。

特点

传输信号:MSIO、MOSI、SCKL、CS

主从结构。SPI 通信由一个主设备(Master)和一个或多个从设备(Slave)组成。主设备控制通信的时序和数据传输,而从设备按照主设备的命令响应数据传输。

同步协议。SPI 使用一个时钟信号(SCLK)来同步数据的传输。主设备产生时钟信号,控制数据传输的速率和时序,而从设备根据时钟信号采样和发送数据。

全双工传输(双向传输)。数据可以同时在主设备和从设备之间双向传输。主设备通过 MOSI(Master Out Slave In)线路发送数据,而从设备通过 MISO(Master In Slave Out)线路接收数据。

多设备支持:SPI 接口可以连接多个从设备,每个从设备使用一个片选信号(SS)来选择与其通信的从设备。主设备通过选择特定的片选信号来与特定的从设备进行通信。

传输速率。SPI 接口的传输速率可以通过调整时钟频率来控制,支持高速传输。传输速率可以根据实际应用需求进行配置,但受硬件和设备的限制。

信号定义

- SCK:Serial Clock,串行时钟

- MOSI:Master Output Slave Input,主发从收

- MISO:Master Input Slave Output,主收从发

- CS/SS:Slave Select / Chip Select,片选信号

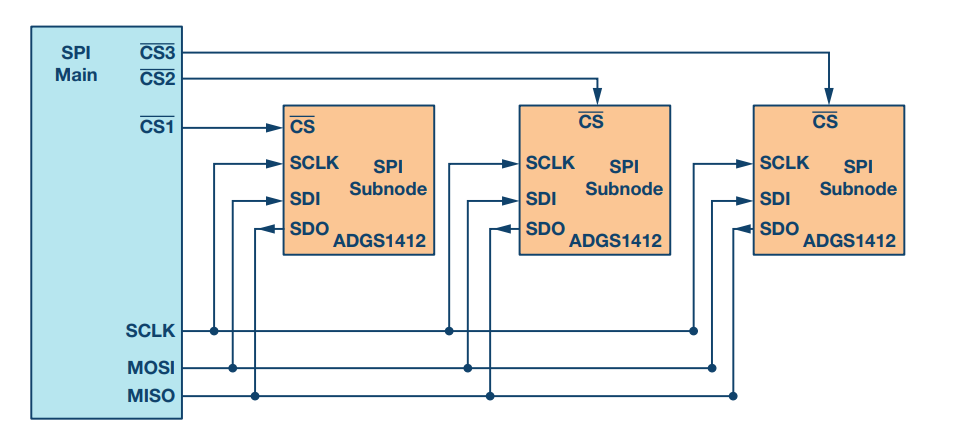

系统框图

对于SPI来讲,通常是一主(MCU)多从(外设),而多个从机是通过CS片选信号线来选择具体和哪一个设备进行通信,从机也将规定片选信号线是高电平有效还是低电平有效

通信过程

不同于I2C,SPI在通信过程中不需要发送起始信号、结束信号,同时也不需要等待应答信号,它的数据线只发送数据,一个byte接着一个byte的数据进行发送。显而易见,它的速度相较于I2C一定是更快的,但是却不能保证数据的可靠性(不能确认从机是否真正收到数据)。另外,在空闲状态的保持和数据发送时的时钟状态上,spi与i2c也是存在差异的。

相位极性

时钟极性(Clock Polarity):定义了在时钟信号在空闲状态下的状态

- 0:在时钟信号的空闲状态时,数据线上保持低电平(0),而在时钟信号激活时传输数据。

- 1:在时钟信号的空闲状态时,数据线上保持高电平(1),而在时钟信号激活时传输数据。

时钟相位(Clock Phase):定义了数据信号采样对应的时钟信号的状态(上升沿/下降沿采样)

- 0:时钟上升沿采样

- 1:时钟下降沿采样

根据相位极性的每种状态,因此对于spi有四种工作模式,具体选择哪一种模式取决于从机支持哪一种。(I2C相位极性是固定的)

设计目的

- 兼容性:不同的设备可能对SPI的极性和相位有不同的要求,选择适当的组合可以确保设备之间的兼容性。

- 时序控制:极性和相位的选择影响了数据传输的时序和同步方式。通过调整极性和相位,可以满足具体应用的时序要求,确保数据的正确传输。

- 信号完整性:正确的极性和相位组合可以减少噪声和时钟抖动对数据传输的影响,提高信号的可靠性和稳定性。

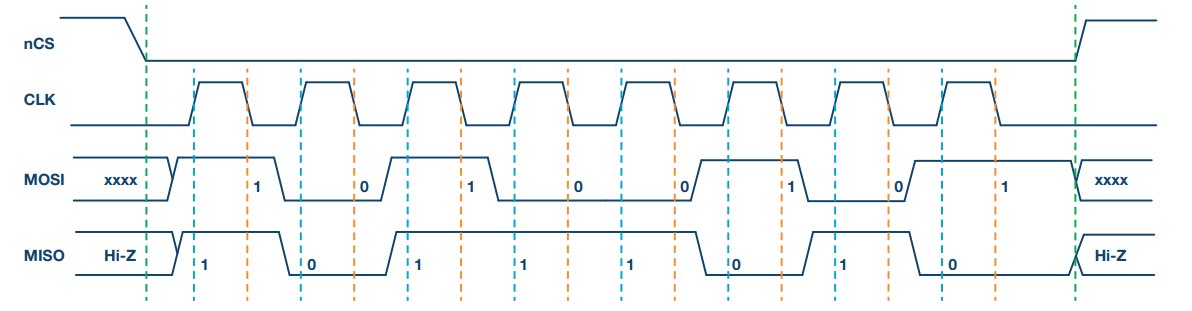

时序

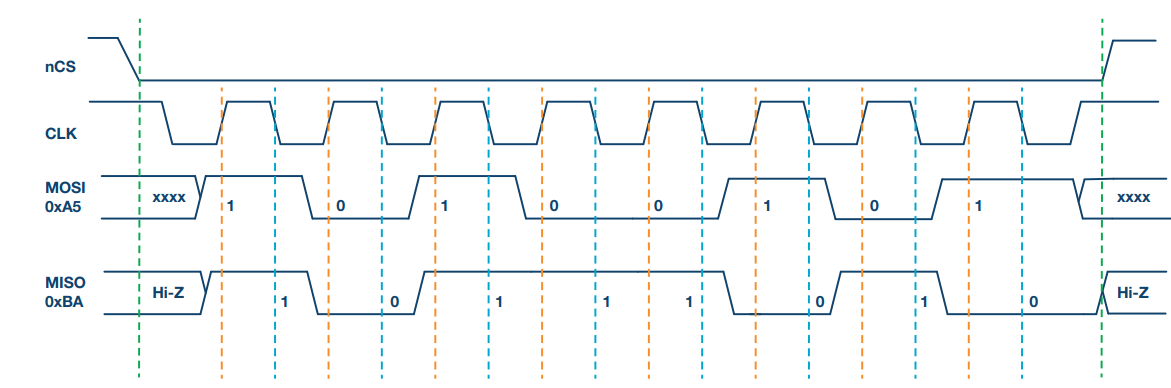

CPOL = 0,CPHA = 0

空闲状态低电平,上升沿采样下降沿从机读数据

CPOL = 0,CPHA = 1

空闲状态低电平,下降沿采样上升沿从机读数据

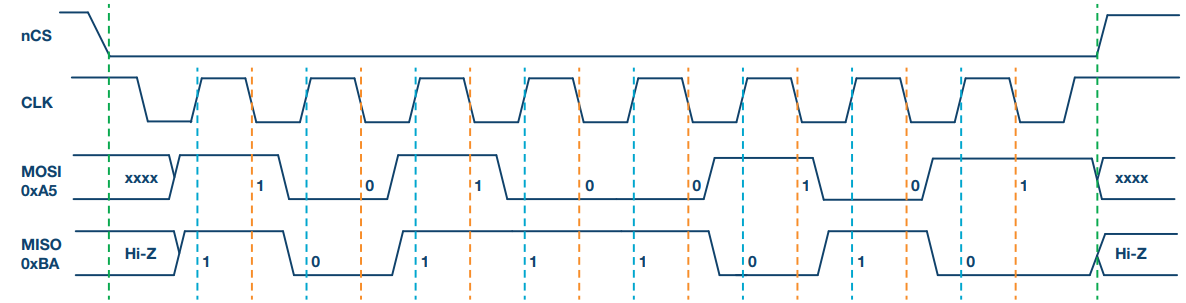

CPOL = 1,CPHA = 0

空闲状态高电平,上升沿采样下降沿从机读数据

CPOL = 1,CPHA = 1

空闲状态高电平,下降沿采样上升沿从机读数据

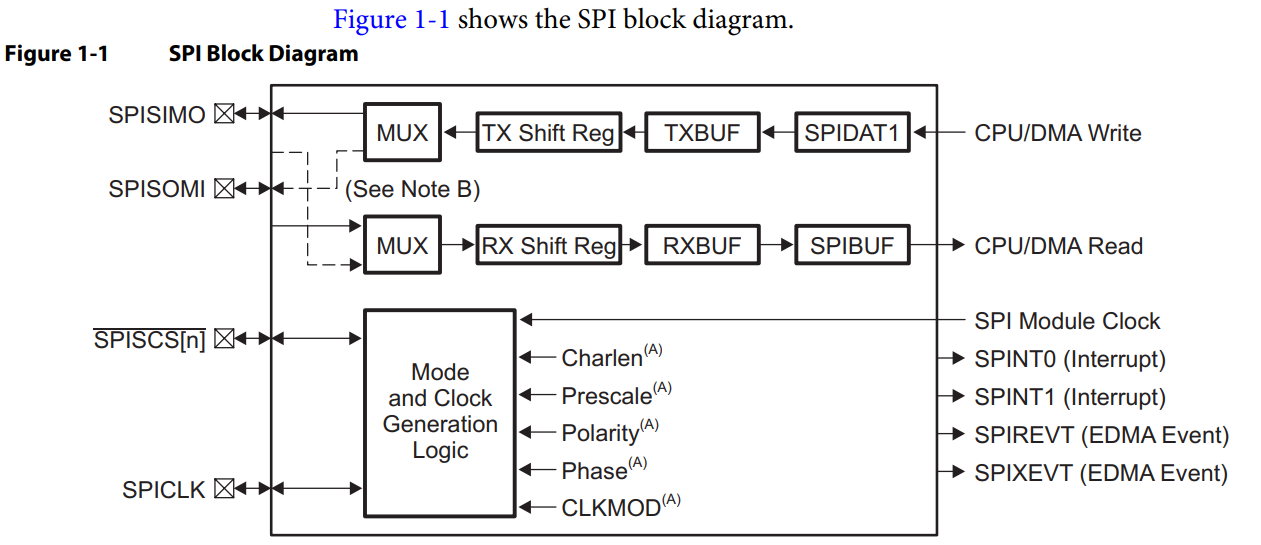

SPI controller

这个是 TI SPI User Guide中的控制器的框图

数据通路

通过读图可以发现,对于控制内部通路存在buffer和移位寄存器。

- 发送数据时,主设备将要发送的数据逐位加载到移位寄存器中,然后通过移位寄存器按照时钟信号的节奏逐位发送。在这个过程中,FIFO缓冲区可以用于存储多个待发送的数据字节,以便在移位寄存器中逐位移动数据之前,提供数据的供应。

- 接收数据时,数据线上的位被移位寄存器接收和存储。如果存在FIFO缓冲区,接收到的数据字节可以先存储在FIFO中,以便在主设备准备好读取时进行传输

配置

时钟SPI控制器产生时钟信号,用于同步数据传输。它通常提供可配置的时钟频率选项,以适应不同的通信速率需求

数据缓冲区SPI控制器提供数据缓冲区,用于存储要发送或接收的数据。它可以是一个单独的寄存器或一个FIFO(First-In-First-Out)缓冲区。

通信模式选择根据从机的需求配置极性和相位以适应其传输模式

中断DMA为了提高传输效率,控制器通常有中断DMA相关的配置等等

TI SSP

串行传输

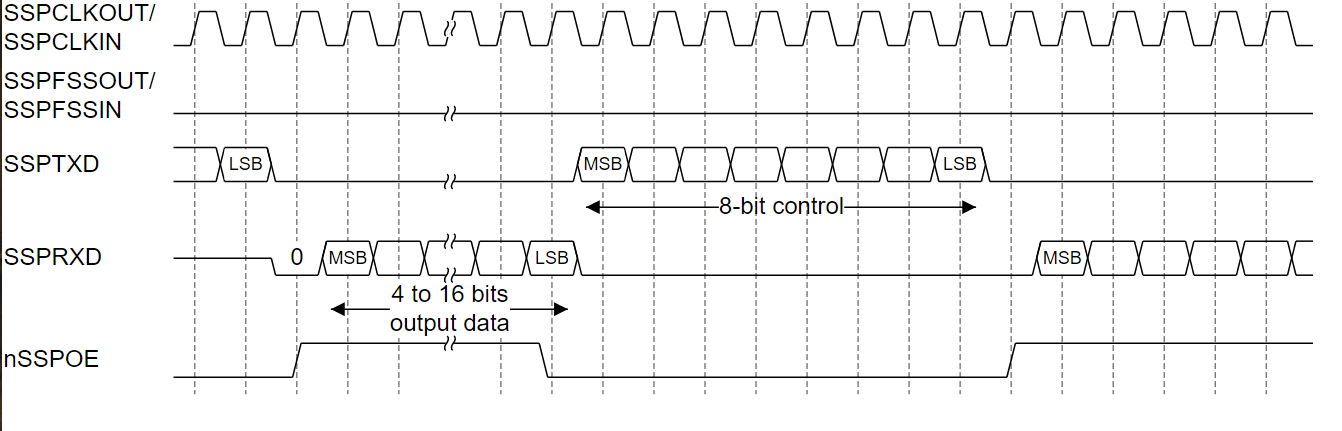

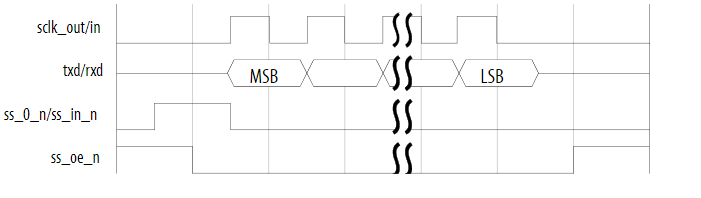

数据传输通过断言帧指示线开始(ss_0_n)一个串行时钟周期。要传输的数据被驱动到txd一个串行时钟周期后行;类似地,来自从机的数据被驱动到接收线。数据在串行时钟的上升沿传播(sclk_输出/slk_输入)并在下降沿捕获。

注:从机选择信号(ss_0_n) 仅当用作从机 SPI 时才有效。对于主 SPI,一旦输出使能信号无效,数据传输就开始。

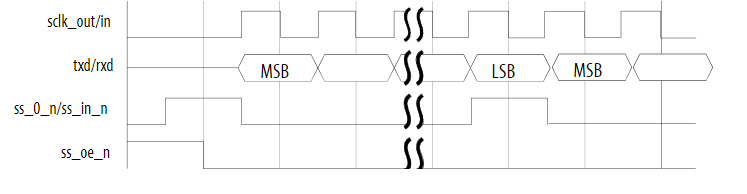

连续传输

连续数据帧的传输方式与单个数据帧相同。在与当前传输的 LSB 相同的周期内,帧指示符在一个时钟周期内被置位,指示接下来是另一个数据帧。

National‘s Microwire

Microwire 格式与 SPI 格式非常相似,不同之处在于传输是半双工而不是全双工,

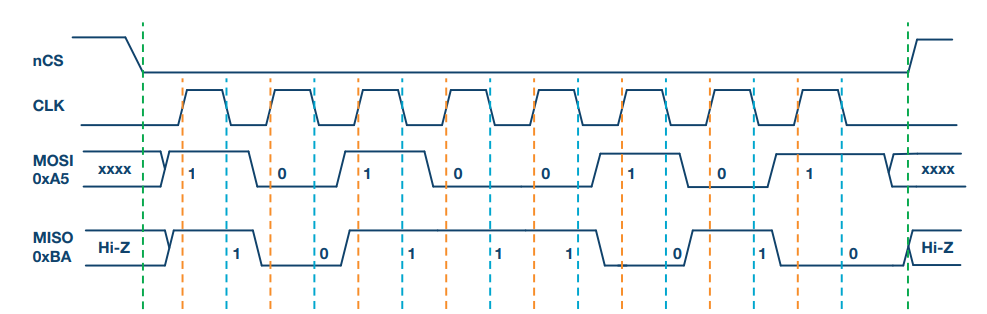

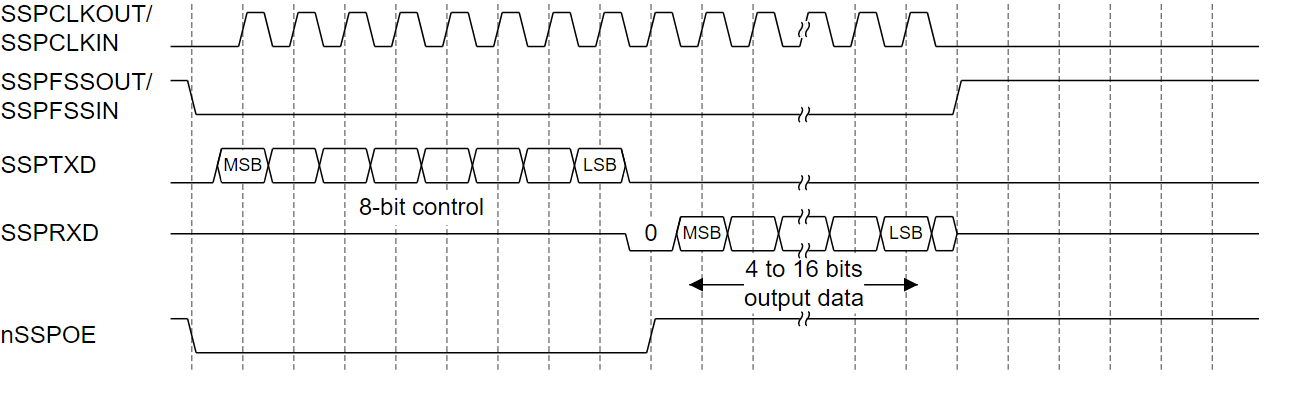

单次传输

使用主从消息传递技术。每个串行传输都以一个 8 位控制字开始,该控制字从 PrimeCell SSP 传输到片外从设备。在此传输期间,PrimeCell SSP 不接收传入数据。消息发送后,片外从机对其进行解码,并在发送 8 位控制消息的最后一位后等待一个串行时钟后,以所需的数据进行响应。返回数据的长度为 4 至 16 位,使得总帧长度在 13-25 位范围内。

在此配置中,在空闲期间:SSPCLKOUT被强制为低电平;SSPFSSOUT被强制为高电平;发送数据线SSPTXD被任意强制为低电平;nSSPOE焊盘使能信号被强制为高电平,使发送焊盘处于高阻抗。

通过将控制字节写入发送 FIFO 来触发发送。SSPFSSOUT的下降沿导致发送 FIFO 底部条目中包含的值被传输到发送逻辑的串行移位寄存器,并且 8 位控制帧的 MSB 被移出到 SSPTXD引脚。SSPFSSOUT在帧传输期间保持低电平。SSPRXD引脚在此传输期间保持三态。

片外串行从设备在每个SSPCLKOUT的上升沿将每个控制位锁存到其串行移位器中。最后一位被从设备锁存后,控制字节在一个时钟等待状态期间被解码,并且从设备通过将数据传输回 PrimeCell SSP 来做出响应。每个位在SSPCLKOUT的下降沿被驱动到SSPRXD线上。PrimeCell SSP 依次锁存SSPCLKOUT上升沿上的每一位。在帧结束时,对于单次传输,SSPFSSOUT信号在最后一位被锁存在接收串行移位器中后一个时钟周期被拉高,这导致数据被传输到接收 FIFO。

连续传输

片外从设备可以在 LSB 被接收移位器锁存后在SSPCLKOUT的下降沿或当SSPFSSOUT引脚变高时使接收线处于三态。

对于连续传输,数据传输的开始和结束方式与单次传输相同。然而,SSPFSSOUT线持续有效,保持低电平,并且数据传输连续发生。下一帧的控制字节紧跟在当前帧接收数据的 LSB 之后。在帧的 LSB 被锁存到 PrimeCell SSP 中之后,每个接收到的值都会在下降沿SSPCLKOUT上从接收移位器传输。